## (19) United States

### (12) Patent Application Publication (10) Pub. No.: US 2022/0207403 A1 KAPIT et al.

Jun. 30, 2022 (43) **Pub. Date:**

### (54) TUNABLE CAPACITOR FOR SUPERCONDUCTING QUBITS

(71) Applicant: COLORADO SCHOOL OF MINES,

Golden, CO (US)

(72) Inventors: Eliot KAPIT, Golden, CO (US);

Nicholas MATERISE, Golden, CO (US); Javad SHABANI, New York

City, NY (US)

(21) Appl. No.: 17/564,789

Dec. 29, 2021 (22) Filed:

### Related U.S. Application Data

(60) Provisional application No. 63/132,831, filed on Dec. 31, 2020.

#### **Publication Classification**

(51) Int. Cl. G06N 10/40 H01L 39/12

(2006.01)(2006.01)

(52)U.S. Cl.

CPC ..... G06N 10/40 (2022.01); H01L 39/12

(2013.01)

#### (57)ABSTRACT

An exemplary tundable capacitor in a quantum system includes a pair of qubits, and a capacitive coupling element coupled between the pair of qubits. The capacitive coupling element includes a plurality of gate terminals. The capacitive coupling element is configured to receive a respective gate voltage at each of the plurality of gate terminals and to adjust a capacitance of the capacitive coupling element in response to the respective gate voltage received at each of the plurality of gate terminals. The capacitance of the capacitive coupling element is configured to control a coupling strength between the pair of qubits.

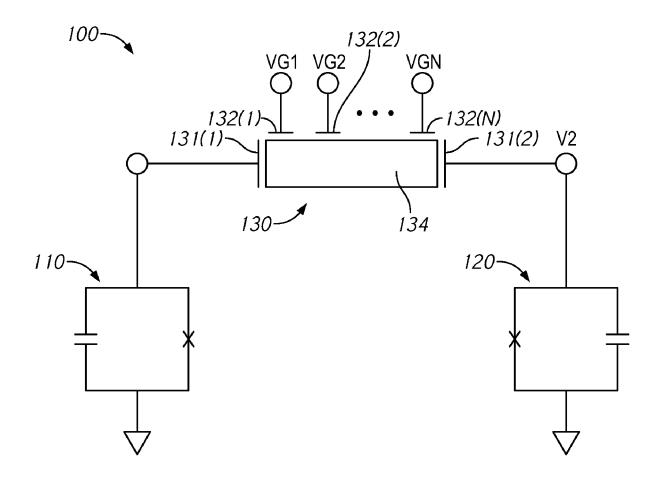

FIG. 1

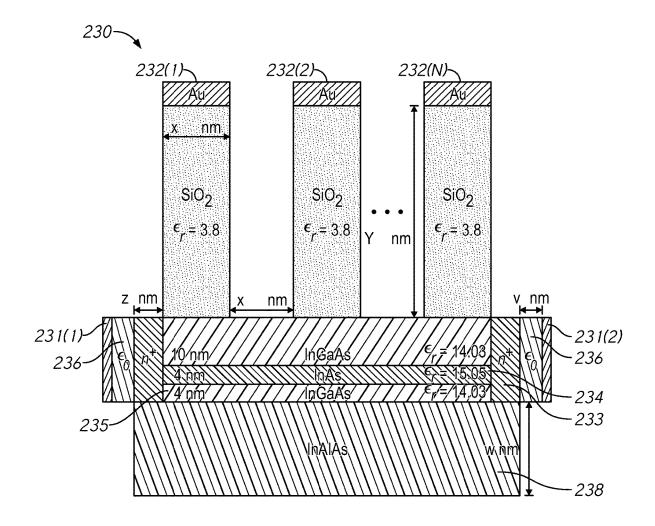

FIG. 2

# TUNABLE CAPACITOR FOR SUPERCONDUCTING QUBITS

## CROSS-REFERENCE TO RELATED APPLICATIONS

[0001] This application claims priority to U.S. Provisional Application No. 63/132,831, filed Dec. 31, 2020, entitled "Tunable Capacitor for Superconducting Qubits Using an InAs/InGaas Heterostructure," the contents of which are incorporated herein in their entirety for all purposes.

### BACKGROUND

[0002] Tunable couplers for superconducting qubits, once a longterm investment in future quantum computers and a direction towards improving two-qubit gate fidelities are now a center-piece of large qubit arrays. The recent quantum supremacy demonstration owes its success in part to the twoqubit gate fidelities across the chip facilitated by fast, tunable couplers. Frequently realized as a mutual inductance or effective capacitance between nearest-neighbor qubits and tuned by flux-biased superconducting quantum interference devices (SQUIDs), these couplers naturally integrate with both fixed and flux-tunable superconducting qubits.

[0003] Recent advancements in semiconductor-superconductor junctions as gate-tunable Josephson junctions have led to new proposals and realizations of coupling schemes to superconducting storage units and readout buses. Unlike their transmon counterparts, these hybrid systems employ various III-V semiconductor materials with properties tunable in both fabrication and with external electric fields as opposed to the canonical, fixed fabrication Al/Al2O3 and Nb-based device stacks that rely on external current sources for tuning.

[0004] As with prior attempts to improve coherence with new materials, there are challenges in realizing high coherence gatemon qubits, where an applied electric potential depletes a superconductor-semiconductor-superconductor junction. Recent dielectric loss studies of III-V materials, specifically Al/GaAs/Al trilayers, suggest that the piezoelectricity of GaAs can contribute to higher losses compared to sapphire or silicon substrates. Apart from the aforementioned experimental results for GaAs, there have been no other studies that have measured the loss in III-V materials at single photon powers and millikelvin temperatures. A solution that addresses both the issue of realizing a fast, tunable coupler and quantifying its potential as an additional source of dielectric loss has proven difficult.

### BRIEF DESCRIPTION OF THE DRAWINGS

[0005] FIG. 1 is a schematic diagram of a 2-qubit quantum system in accordance with embodiments of the present disclosure.

[0006] FIG. 2 is a cross-sectional diagram of capacitive coupling element in accordance with embodiments of the disclosure.

### DETAILED DESCRIPTION

[0007] This disclosure includes examples of a tunable coupler to control interactions between solid-state qubits, including interactions between solid-sate qubits in a single, two-dimensional (2D) layer, interactions between three-dimensional (3D) cavities, or any combination thereof . In some examples, the solid-state qubits may include super-

conducting qubit, quantum-dot qubits, flux-qubits, 3D cavities, or any other type of solid-state qubits. The tunable coupler may include a capacitor with source and drain terminals each connected to a respective qubit, and a plurality of gate terminals that are selectively enabled to adjust or control a capacitance. In some examples, adoption of fast, parametric coupling elements may improve the performance of superconducting qubits. A low loss, high contrast coupler may be useful in scaling up quantum computing systems. In some examples, the gate-tunable coupler may be formed using a two-dimensional electron gas in an InAs/InGaAs heterostructure. Such an implementation may yield an on/off ratio of over two orders of magnitude.

[0008] The gate voltage-controlled capacitive coupling element between neighboring superconducting qubits described herein may include a pair of fixed air-gap capacitors with a single, effective capacitance that is tuned by a collection of gates (e.g., metal oxide) that deplete a two-dimensional electron gas (2DEG) in a semiconductor heterostructure (e.g., InAs/InGaAs heterostructure). The described coupling element relying on tuning of electric fields to control qubit interactions may be a replacement for a flux-biased superconducting quantum interference device (SQUID)-based inductive couplers (which rely on tuning of electromagnetic fields to control qubit interactions).

[0009] Air-gap capacitors isolate the tuning elements, namely the gates, from the qubits, which may reduce stray electric fields on the neighboring qubits as compared with flux-biased SQUID devices, where stray magnetic fields lead to cross-talk between qubits. In some examples, implementations other than the air-gap capacitors may be realized to achieve a tunable capacitor without departing from the scope of the disclosure.

[0010] FIG. 1 is a schematic diagram of a 2-qubit quantum system 100 in accordance with embodiments of the present disclosure. The system 100 includes a first qubit  $110,\,$  a second qubit  $120,\,$  and a capacitive coupling element 130. The first qubit 110 and the second qubit 120 may form a pair of qubits for which the capacitive coupling element 130 is used to control coupling there between. The first qubit 110 and the second qubit 120 may include any type of transmon qubit.

[0011] The capacitive coupling element 130 may include source/drain terminals 131(1)-(2) at each end that are coupled to the nodes providing the V1 and V2 voltages, respectively. The capacitive coupling element 130 may further include multiple gate terminals 132(1)-(N), where N is a positive integer. In some examples, N may be equal to 3, 4, 5, etc. In some examples, N may be less than 10. In some examples, the capacitive coupling element 130 may include only two gate terminals. The gate terminals 132(1)-(N) may be configured to control the conductive properties within the dielectric material 134 to control the effective capacitance of the capacitive coupling element 130. Each of the gate terminals 132(1)-(N) may be configured to receive a respective gate voltage VG1-VGN. Collectively, the respective VG1-VGN gate voltages may be selected to tune a particular effective capacitance of the capacitive coupling element 130 between the source/drain terminals 131(1)-(2). [0012] In operation, the VG1-VGN gate voltages may be selected to control coupling between the first qubit 110 and the second qubit 120 by adjusting the capacitance of the capacitive coupling element 130. That is, as the VG1-VGN gate voltages increase, the coupling between the first qubit 110 and the second qubit 120 become tighter, because the capacitance increases within the capacitive coupling element. Implementation of the capacitive coupling element 130 may be a replacement for a flux-biased SQUID-based inductive couplers, and may reduce crosstalk between the field controlling the coupler and the qubits, particularly if the qubits are tunable with magnetic flux.

[0013] In some examples, alternatively or additionally, the capacitive coupling element may be configured to adjust the capacitance in response to the alternating-current (AC) fields to perform parametric operations. In some examples, first and second qubits 110 and 120 and the capacitive coupling element 130 may be included in a small logical qubit device. In some examples, one of the pair of qubits may be a solid-state qubit and the other may be a three-dimensional cavity. In some examples, the capacitive coupling element may be configured to adjust the capacitance of the capacitive coupling element to route a signal between the first and qubits 110 and 120. In a multi-qubit architecture on a chip with multiple ones of the tunable elements, the tunable elements may be configured to route singals around the chip for any purpose.

[0014] FIG. 2 is a cross-sectional diagram of capacitive coupling element 230 in accordance with embodiments of the disclosure. The capacitive coupling element 130 of FIG. 1 may implement the capacitive coupling element 230 in some examples. The capacitive coupling element 230 may include source/drain terminals 231(1)-(2) at each end. The capacitive coupling element 230 may further include multiple gate terminals 232(1)-(N) (e.g., Au and SiO<sub>2</sub>), where N is a positive integer. In some examples, N may be equal to 3, 4, 5, etc. In some examples, N may be less than 10. In some examples, the capacitive coupling element 230 may include only two gate terminals. In some examples, the gate terminals 232(1)-(N) may have a width of X nm and height of Y nm. In some examples, X may be greater than Y. In some examples, X is twice as great as Y. The distances between adjacent gate terminals 232(1)-(N) may be the same as the width, which is X nm.

[0015] The gate terminals 232(1)-(N) may be configured to control the conductive properties within the dielectric material 234 (e.g., InAs) and 235 (e.g., InGaAs) formed on the substrate 238 (e.g., InAIAs) to control the effective capacitance of the capacitive coupling element 230. The substrate 238 may have a height of W nm. Each of the gate terminals 232(1)-(N) may be configured to receive a respective gate voltage VG1-VGN. Collectively, the respective VG1-VGN gate voltages may be selected to tune a particular effective capacitance of the capacitive coupling element 230 between the source/drain terminals 231(1)-(2).

[0016] The dielectric material 234 and 235 may be buffered on each side by respective n+ regions 233 and air-gap regions 236. The air gap regions 236 may be in contact with the source/drain terminals 231(1)-(2). The n+ region 233 may include highly doped n-type InAs. The n+ regions 233 may also be formed on the substrate 238, and may have a width of Z nm. The air-gap regions 236 may have a width of V nm. In some examples, V is less than Z. In some examples, Z is 3, 4, or 5 times greater than V. In some examples, X is four times greater than Z.

[0017] Appendix A includes specific, non-limiting examples of the capacitive coupling element described herein. The contents of Appendix A are incorporated herein in their entirety for all purposes.

[0018] From the foregoing it will be appreciated that, although specific embodiments of the disclosure have been described herein for purposes of illustration, various modifications may be made without deviating from the spirit and scope of the disclosure. Accordingly, the disclosure is not limited except as by the appended claims.

- 1. An apparatus, comprising:

- a pair of qubits; and

- a capacitive coupling element coupled between the pair of qubits and comprising a plurality of gate terminals, wherein the capacitive coupling element is configured to receive a respective gate voltage at each of the plurality of gate terminals and to adjust a capacitance of the capacitive coupling element in response to the respective gate voltage received at each of the plurality of gate terminals, wherein the capacitance of the capacitive coupling element is configured to control a coupling strength between the pair of qubits.

- 2. The apparatus of claim 1, wherein the capacitive coupling element includes a fixed air-gap capacitor.

- 3. The apparatus of claim 2, wherein the fixed air gap capacitor includes a source terminal and a doped n-type region separated by an air-gap region.

- **4**. The apparatus of claim **3**, wherein a width of the doped n-type region is greater than a width of the air-gap region.

- 5. The apparatus of claim 1, wherein the capacitive coupling element includes an Indium-Arsenide (InAs)/Indium gallium arsenide (InGaAs) semiconductor heterostructure

- 6. The apparatus of claim 1, wherein the plurality of gates terminals includes at least three gate terminals.

- 7. The apparatus of claim 1, wherein a gate terminal of the plurality of gates terminals comprises a layer of silicon dioxide and a layer of gold.

- **8**. The apparatus of claim **1**, wherein a width of a gate terminal of the plurality of gates terminals is greater than a height of the gate terminal.

- 9. The apparatus of claim 1, wherein the capacitive coupling element is formed on a substrate.

- 10. The apparatus of claim 1, wherein the pair of qubits includes a pair of transmon qubits.

- 11. The apparatus of claim 1, wherein the pair of qubits includes a pair of flux qubits.

- 12. The apparatus of claim 1, wherein the pair of qubits are in a single, two-dimensional layer of a multi-qubit architecture.

- 13. The apparatus of claim 1, wherein the pair of qubits are each a respective one of a different three-dimensional cavity of a multi-qubit architecture.

- 14. The apparatus of claim 1, wherein the capacitive coupling element is configured to adjust the capacitance of the capacitive coupling element in response to the alternating-current (AC) fields to perform parametric operations.

- 15. The apparatus of claim 1, wherein the pair of qubits and the capacitive coupling element are included in a small logical qubit device.

- 16. The apparatus of claim 1, wherein one of the pair of qubits is a solid-state qubit or cavity to a two-dimensional or a three-dimensional cavity of the other qubit.

- 17. The apparatus of claim 1, wherein the capacitive coupling element is configured to adjust the capacitance of the capacitive coupling element to route a signal between the pair of qubits.

\* \* \* \* \*